蜂鸟 E200 是一个处理器系列,包含了多款不同的具体处理器型号。所有的 E200 系列处理器核均支持协处理器接口,可用于自定义扩展指令

– E201 核是面积 小的核,可 以配置为 RV32IC RV32EC 架构,不支持其他的

展指令子集。

– E203 核可以配置为 RV32IMAC 或者 RV32EMAC 架构,使用面积优化的多周期硬件乘除法单元。

– E205 核为 RV32IMAC 架构, 使用单周期 硬件乘法单元和多周期的硬件除法单元

– E205f 核为 RV32IMAFC 架构,在基本的 E205 基础上加入了单精度浮点运算单元

– E205fd核为 RV32IMAFDC 架构 ,在基本 E205 基础上加入了单精度和双精度浮点运算单元。

蜂鸟E200处理器有一定的可配置性,可在e200_opensource/rtl/e203/core/config.v中进行更改,核配置选项可在官方手册中查询

目录组织结构剖析

- rtl 存放RTL目录

- tb 测试平台目录

- vsim 仿真目录

- fpga FPGA项目脚本目录

- riscv-tools 存放工具目录

- doc 文档

WINDOWS环境下工作环境配置

因为Windows环境下的bash操作和LINUX不同,故原来写的Makefile不再可用,因此不能简单通过文档中的 make install 来进行安装,所以我们有两个选择

– 重写Makefile,修改为Windows CMD指令

– 读懂Makefile在干啥,然后手动操作一遍

本教程取后面的方法。首先获得调试FPGA所需要的核心Verilog文件

Makefile对于install参数的定义如下:

install:

mkdir -p install

cp ../rtl/${CORE} ${INSTALL_RTL} -rf

cp ${FPGA_DIR}/src/system.org ${INSTALL_RTL}/system.v -rf

sed -i 's/e200/${CORE}/g' ${INSTALL_RTL}/system.v

sed -i '1i\`define FPGA_SOURCE\' ${INSTALL_RTL}/core/${CORE}_defines.v

EXTRA_FPGA_VSRCS :=

verilog := $(wildcard ${INSTALL_RTL}/*/*.v)

verilog += $(wildcard ${INSTALL_RTL}/*.v)

为你的Verilog创建一个文件夹,名字任意

– 第一步:再e200_opensource-master/rtl/e203中复制所有的文件夹到你的工作目录

– 第二步:打开e200_opensource-master/fpga文件夹,找一个跟你的板子贴合最近的文件夹,把里面的文件复制出来到你的工作目录

– 第三步:把system.org 文件名后缀改成 .v 文件

至此 工作目录配置完毕。

WINDOWS环境下Vivado工程的建立

建立Vivado工程

打开Vivado,新建工程,选择你的芯片

添加设计文件->添加文件夹->选择你的工作目录文件夹,vivado会自动分析你的文件关联并设置顶层文件。

补全所需IP核文件

在原来的编译过程中,采用了TCL指令对IP核进行创建和例化,在Windows中的Vivado环境,需要手动添加IP核。

TCL指令目录:

e200_opensource-master\fpga\artydevkit\script

IP核生成的TCL指令见ip.tcl

源码如下

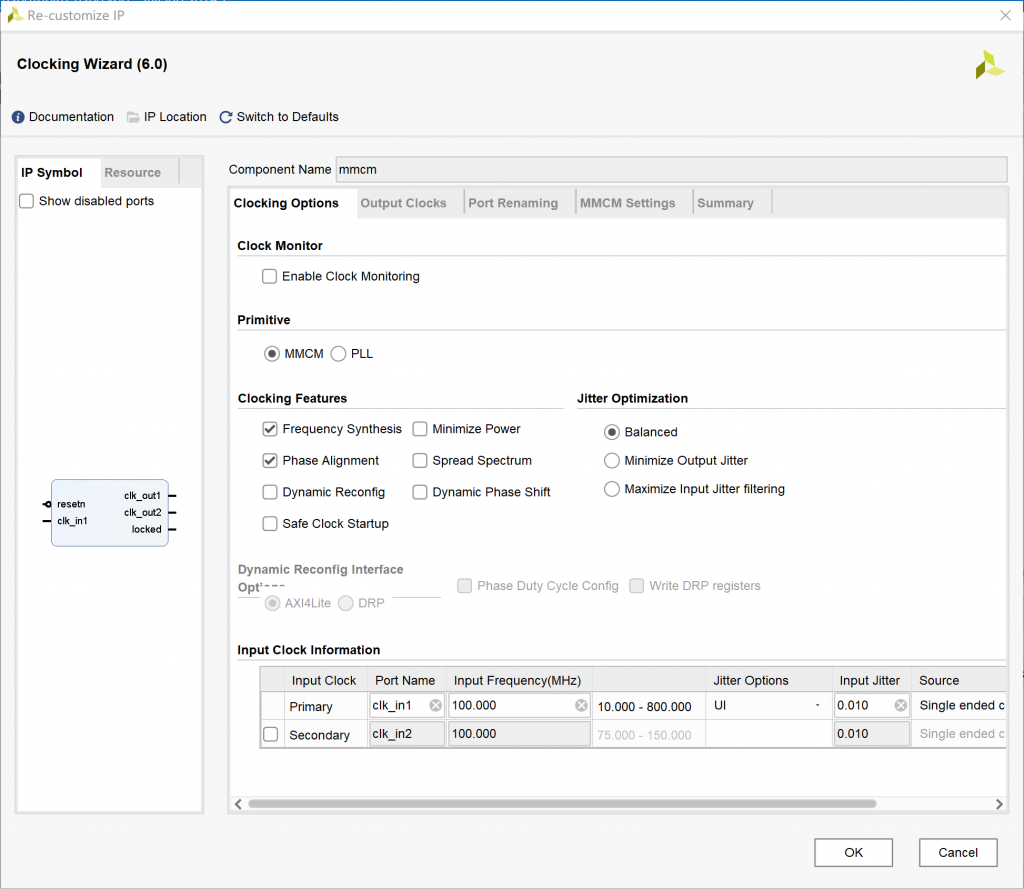

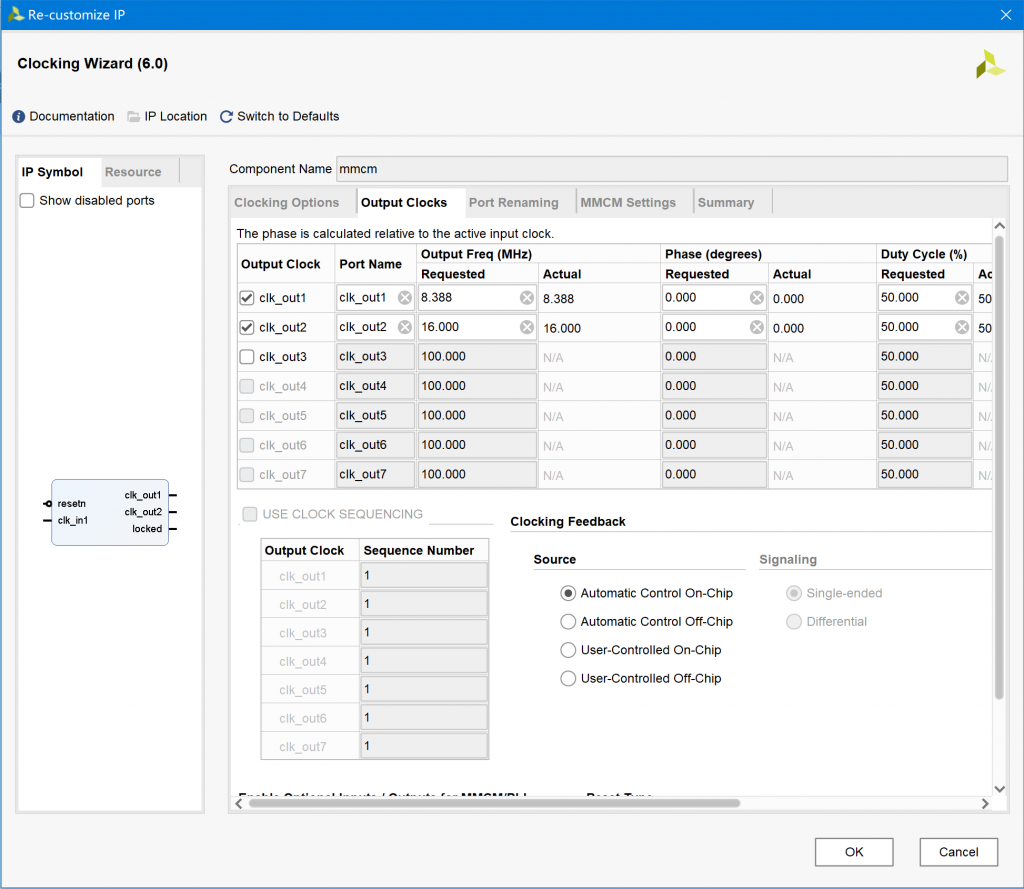

create_ip -vendor xilinx.com -library ip -name clk_wiz -module_name mmcm -dir $ipdir -force

set_property -dict [list \

CONFIG.PRIMITIVE {MMCM} \

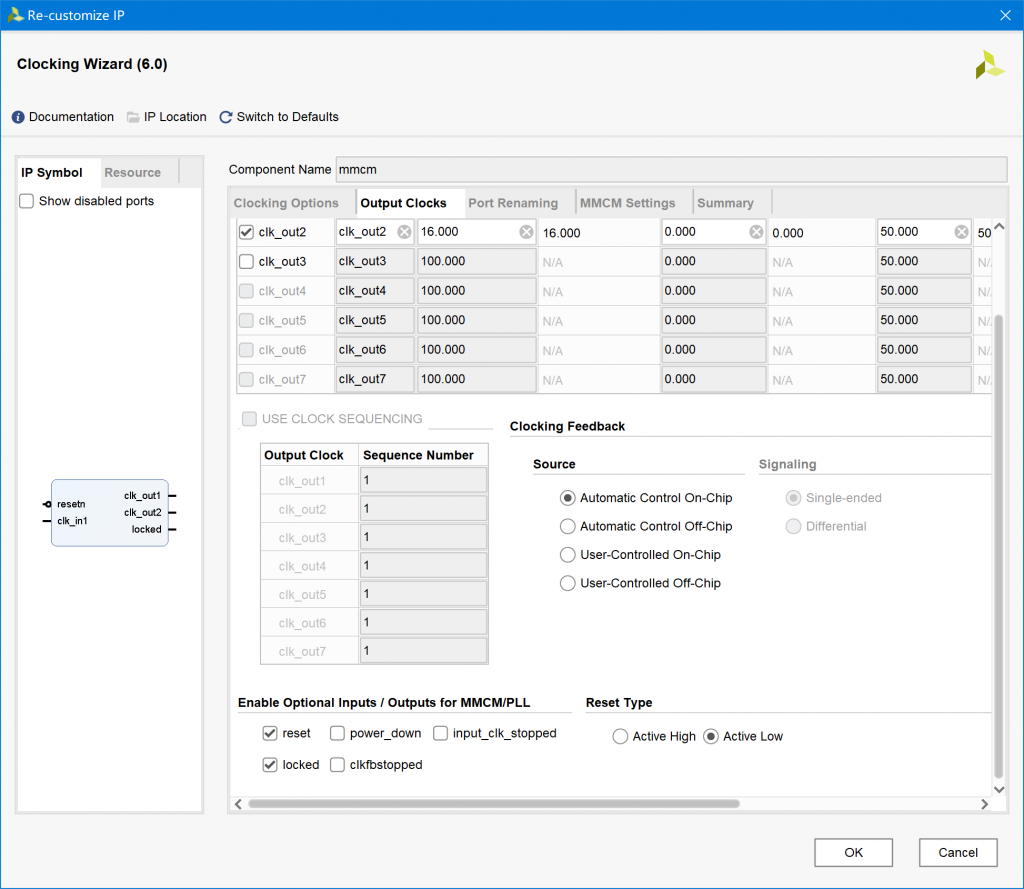

CONFIG.RESET_TYPE {ACTIVE_LOW} \

CONFIG.CLKOUT1_USED {true} \

CONFIG.CLKOUT2_USED {true} \

CONFIG.CLKOUT1_REQUESTED_OUT_FREQ {8.388} \

CONFIG.CLKOUT2_REQUESTED_OUT_FREQ {16.000} \

] [get_ips mmcm]

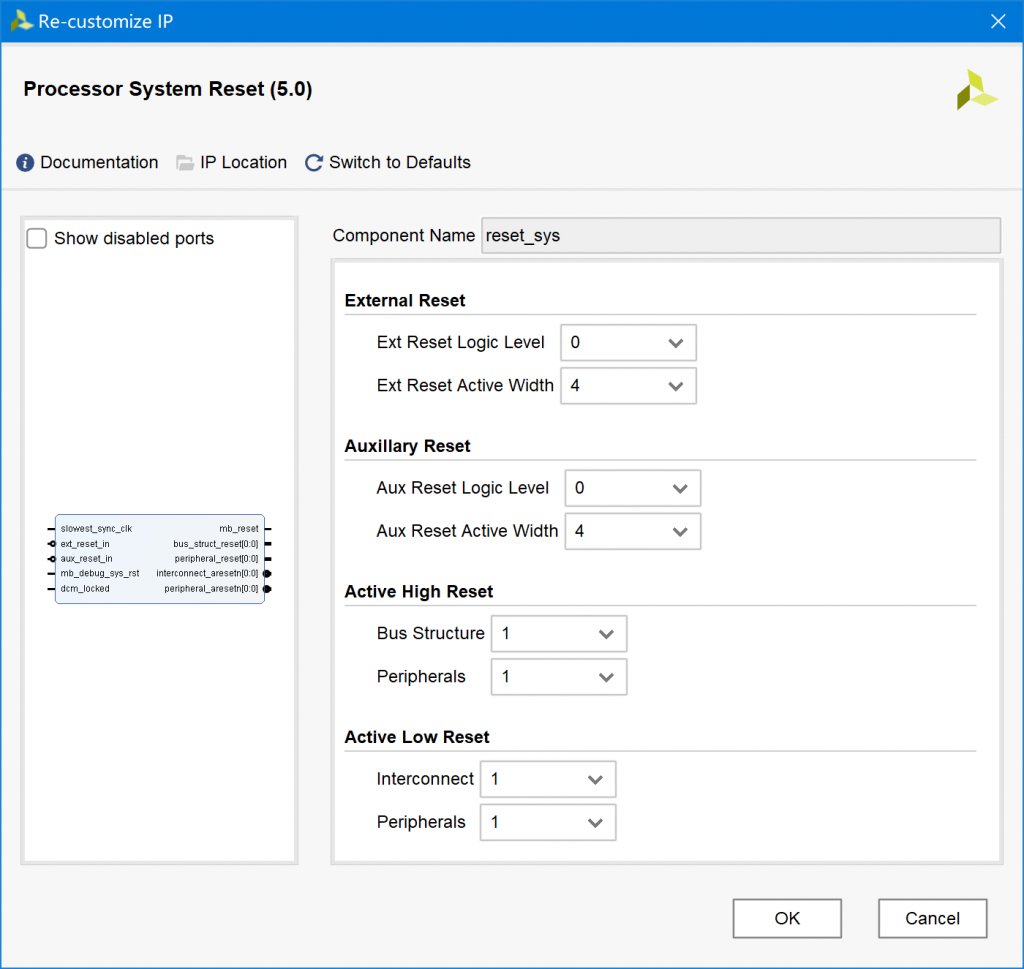

create_ip -vendor xilinx.com -library ip -name proc_sys_reset -module_name reset_sys -dir $ipdir -force

set_property -dict [list \

CONFIG.C_EXT_RESET_HIGH {false} \

CONFIG.C_AUX_RESET_HIGH {false} \

CONFIG.C_NUM_BUS_RST {1} \

CONFIG.C_NUM_PERP_RST {1} \

CONFIG.C_NUM_INTERCONNECT_ARESETN {1} \

CONFIG.C_NUM_PERP_ARESETN {1} \

] [get_ips reset_sys]

这里定义了两个IP核 一个用于配置全局时钟clk_wiz,另一个用于处理全局复位信号sys_reset

先来添加全局时钟IP核

IP Catalog->搜索clock 找到clocking wizard

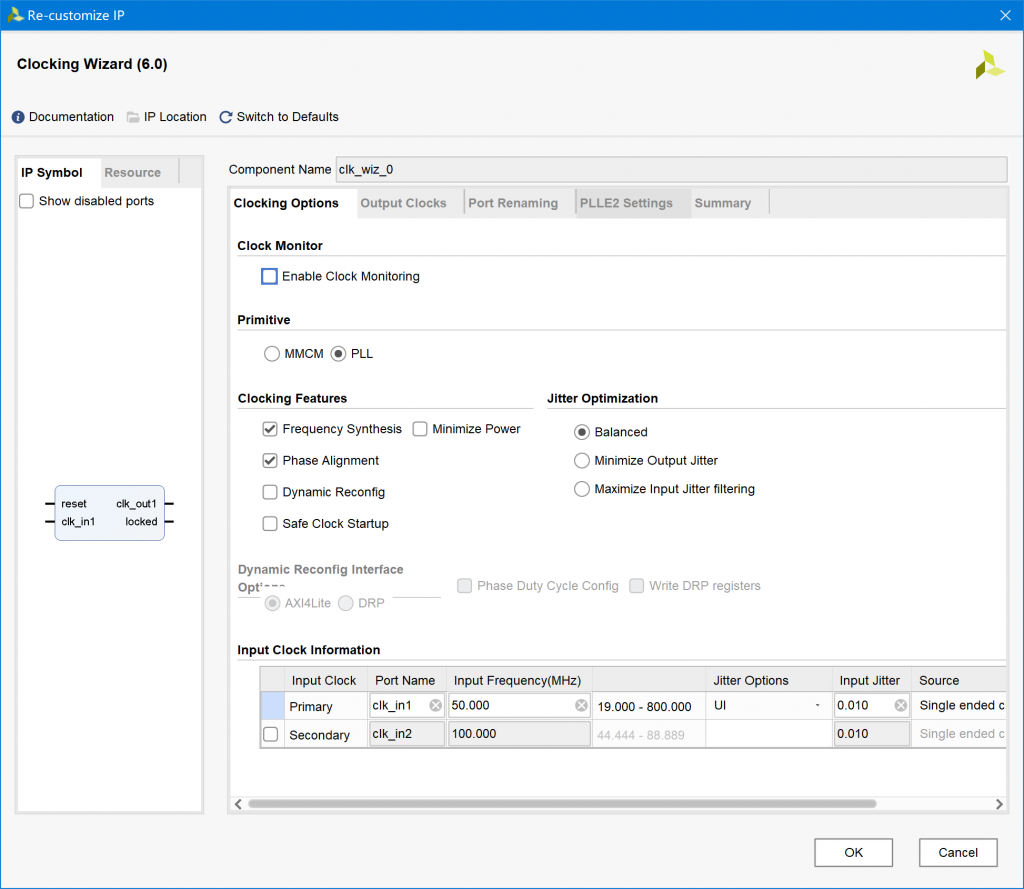

选择类别MMCM,输入100MHz的信号,输出8.388MHz和16MHz的分频信号,带复位和lock脚,复位低电平使能。命名为mmcm

具体配置如下:

再来添加全局复位IP核

IP Catalog->搜索reset->选择Processor System Reset IP核

配置为低电平使能,位宽1,命名为reset_sys

具体配置如下:

根据自己板载时钟适配

适配方式:添加PLL锁相环

IP Catalog->搜索clock 找到clocking wizard

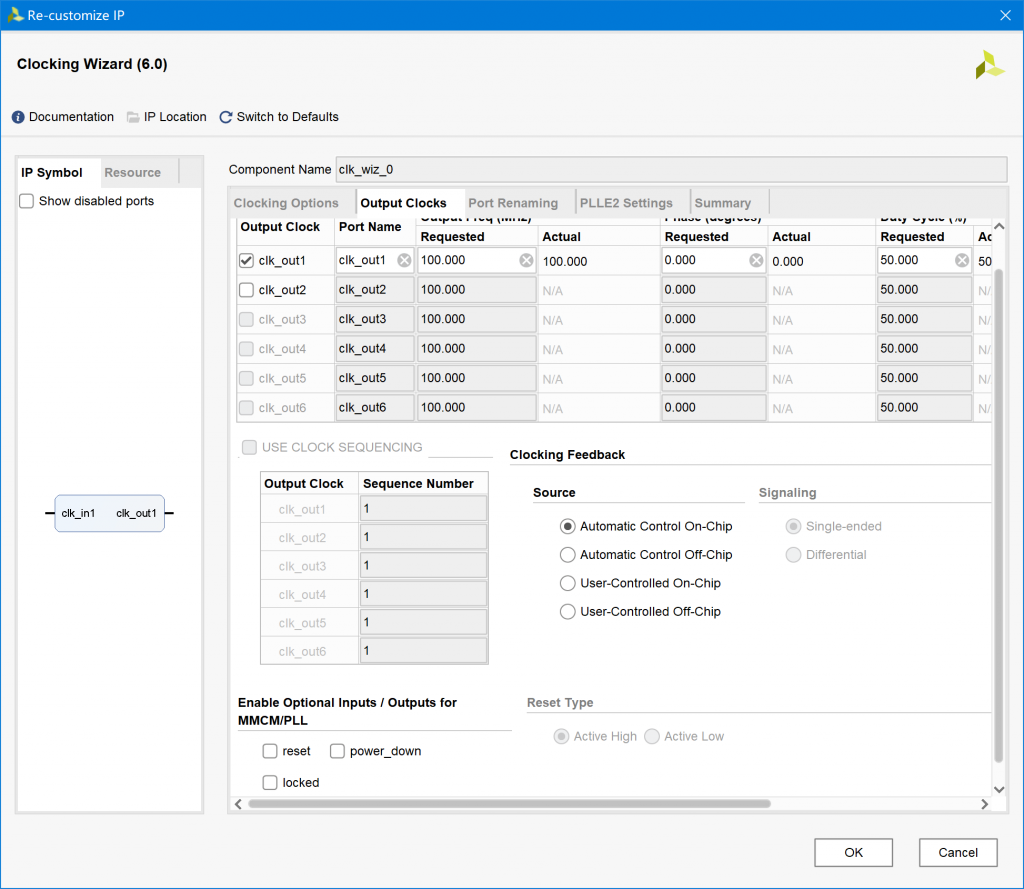

选择类别PLL,输入信号你板子时钟频率,输出100MHz,为了简单不带复位,不带lock。

具体配置如下:

加了这个以后需要修改system.v顶层文件

例化clk_wiz_0

wire CLK100MHZ;

clk_wiz_0 clk(

.clk_in1(CLK50MHZ),

.clk_out1(CLK100MHZ)

)

同时将开头的

input wire CLK100MHZ,//GCLK-W19

input wire CLK32768KHZ,//RTC_CLK-Y18

里面的CLK100MHZ改为CLK50MHZ。

修改IOBUF原语

system.v里面有大量IOBUF原语。IOBUF原语用于初始化双向输入输出引脚,大概长这个样子

//=================================================

// IOBUF instantiation for GPIOs

wire iobuf_gpio_0_o;

IOBUF

#(

.DRIVE(12),

.IBUF_LOW_PWR("TRUE"),

.IOSTANDARD("DEFAULT"),

.SLEW("SLOW")

)

IOBUF_gpio_0

(

.O(iobuf_gpio_0_o),

.IO(gpio[0]),

.I(dut_io_pads_gpio_0_o_oval),

.T(~dut_io_pads_gpio_0_o_oe)

);

assign dut_io_pads_gpio_0_i_ival = iobuf_gpio_0_o & dut_io_pads_gpio_0_o_ie;

其中 上面的#部分用于对引脚进行初始化定义

下面的IOBUF如下:

– .O 输出buffer

– .IO 物理管脚约束

– .I 输入buffer

– .T 反

– 根据自己的需要搞吧

将IOBUF的GPIO约束到物理设备

直接 assign YOUR_DEVICE = gpio[x]

就能用GPIO控制你的外设啦!

当然,你要在你的顶层文件里例化你的外设,或者端口把这个输出出去。

总的来说gpio数组即是一切。。

比如:

assign LED[0]=gpio[0]

写约束文件 约束物理管脚

写*.xdc文件作为物理约束,大概格式如下

set_property IOSTANDARD LVCMOS33 [get_ports RST]

set_property PACKAGE_PIN L16 [get_ports RST]

get_ports 里面改成你在顶层文件输出引脚

PACKAGE_PIN 后面改成你想约束到的硬件端口

修改完约束以后,还要进行最后一步操作,因为E203的核引出的引脚实在太多了,有些我们并没有约束出来,在Vivado中会出现错误提示 [DRC NSTD-1] 大概就是一坨提示五六行然后后面接了几个端口号说你没有约束。

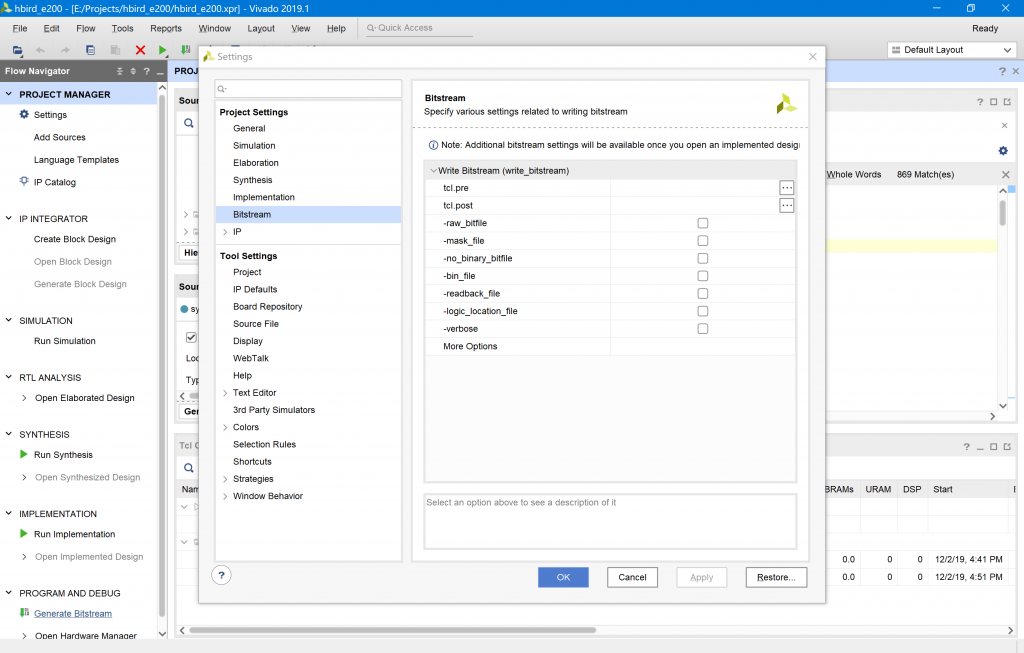

为了解决这个问题需要写一个TCL预编译指令

新建一个记事本,里面输入

set_property SEVERITY {Warning} [get_drc_checks NSTD-1]

set_property SEVERITY {Warning} [get_drc_checks RTSTAT-1]

set_property SEVERITY {Warning} [get_drc_checks UCIO-1]

关闭,修改扩展名为.tcl文件

回到Vivado,右击Generate bit stream 在Prebuild script里面选中你写的tcl文件。

进行比特文件编译,并烧录至FPGA

至此,蜂鸟E200 RISCV-CPU在Windows环境便可编译成功。

发表回复